Circuite Digitale - proiect

Reguli pentru desfasurarea activitatilor didactice

• Conform reglamentului universitar si a contractului de studii semnat anual de catre fiecare student, prezenta la orele de proiect este facultativa;

• Proiectele sunt individuale, atat din punctul de vedere al cerintei cat si al rezolvarii!

• La inceputul semestrului (dar nu mai tarziu de modulul 2), studentul poate propune ca proiect orice aplicatie cu circuite digitale. In lipsa acestei propuneri, i se va aloca "la intamplare" un subpunct al unei probleme de mai jos.

• Notarea se va face cel tarziu in ultima ora de proiect din semestru, in urma unei discutii libere si publice intre student si cadrul didactic. Se vor urmari urmatoarele puncte:

- rezolvarea teoretica a problemei, pana la obtinerea relatiilor necesare desenarii schemei electronice - (3p),

- desenarea schemei electronice intr-un pachet software adecvat (Orcad/Xilinx ISE/Altium/Eagle/etc.) si simularea circuitului - (3p),

- proiectarea unui cablaj imprimat pentru solutia propusa, intr-un pachet software adecvat - (3p),

- aspectul estetic al proiectului scris - (1p).

• Implementarea problemei intr-un circuit programabil FPGA este echivalenta cu desenarea si simularea schemei electronice in orice alt mediu CAD.

• Pentru nota maxima NU este obligatorie realizarea practica a circuitului electronic; daca studentul doreste totusi realizarea practica, va fi sprijinit in masura posibilitatilor. Realizarea unui circuit experimental functional este echivalenta cu simularea + proiectarea cablajului pentru circuitul respectiv.

Prin parcurgerea acestui proiect, studentul ar trebui:

• sa utilizeze cunostintele acumulate la materia Circuite Digitale;

• sa inteleaga pasii esentiali de proiectare ai unui circuit electronic digital;

• sa exerseze utilizarea pachetelor CAD din domeniul electronic;

• sa poata proiecta un cablaj electronic utilizabil (!) pornind de la schema electronica cu circuite digitale;

• sa prezinte in mod clar efortul depus la rezolvarea proiectului, precum si rezultatele obtinute.

Resurse:

Gasiti mai jos problemele folosite pana acum ca tema de proiect. Problemele vechi pot fi folosite ca sursa de inspiratie pentru proiecte noi, insa nu vor exista doua teme identice. Situatia alocarii temelor se afla doar la cadrul didactic.

Cateva exemple rezolvate sunt prezentate la sfarsitul paginii.

Anul universitar 2013-2014:

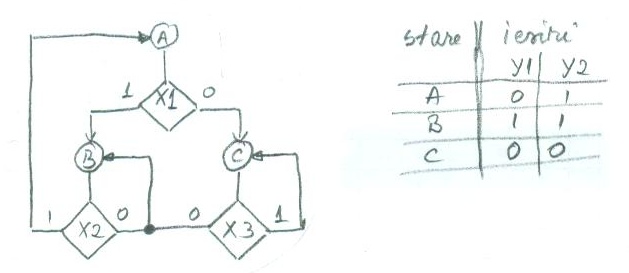

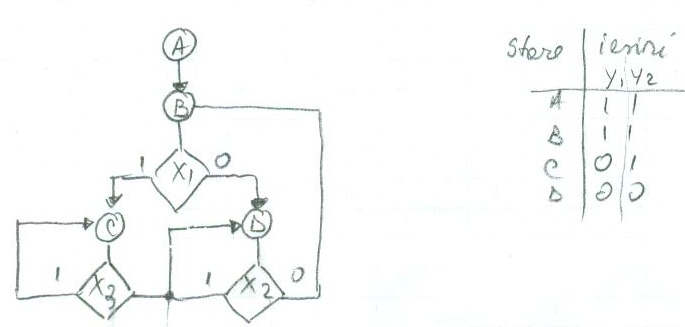

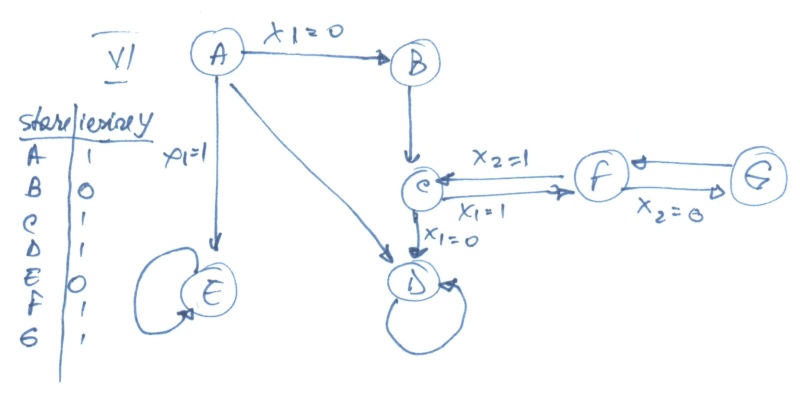

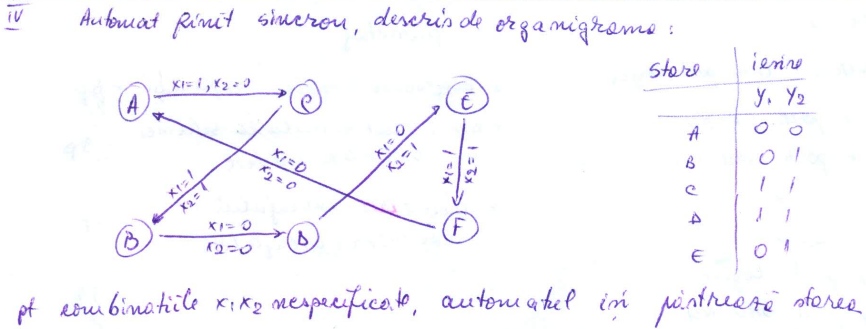

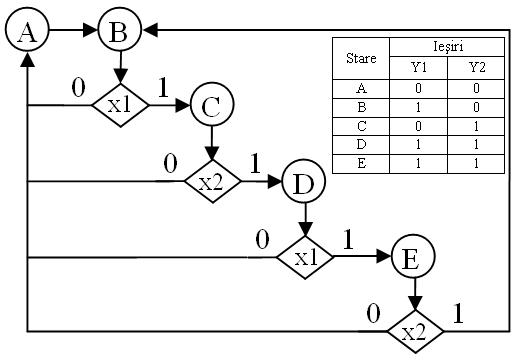

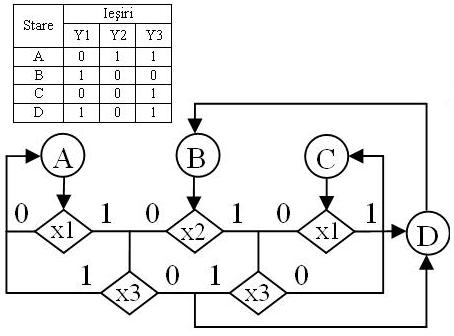

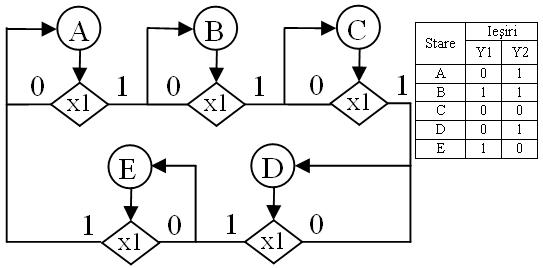

Cerinta: Sa se implementeze automatul finit din figura anterioara, utilizand doar:

1) circuite bistabile D si porti logice;

2) circuite bistabile D si porti logice SI/SI-nu;

3) circuite bistabile D si porti logice SAU/SAU-NU;

4) circuite bistabile D si multiplexoare;

5) circuite bistabile D si decodificatoare;

6) circuite bistabile JK si porti logice;

7) circuite bistabile JK si porti logice SI/SI-NU;

8) circuite bistabile JK si porti logice SAU/SAU-nu;

9) circuite bistabile JK si multiplexoare;

10) circuite bistabile JK si decodificatoare;

Anul universitar 2012-2013:

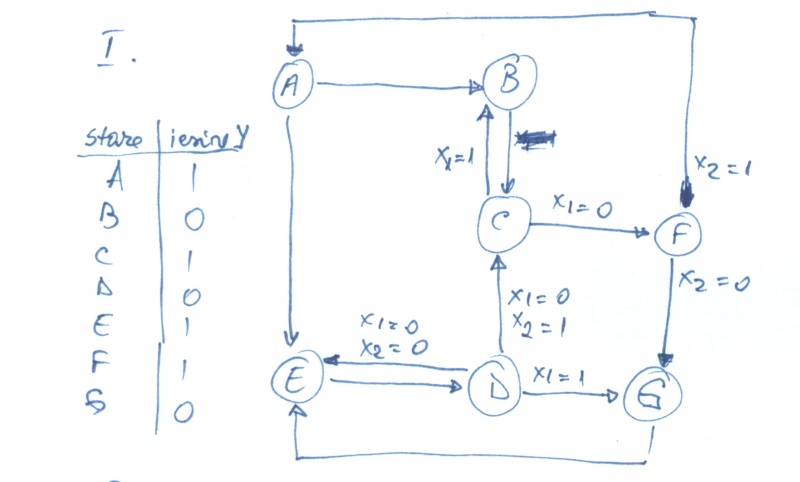

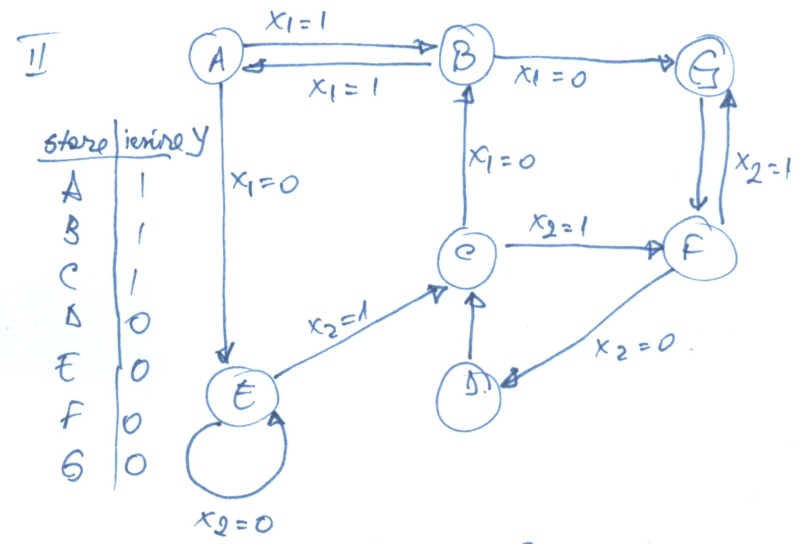

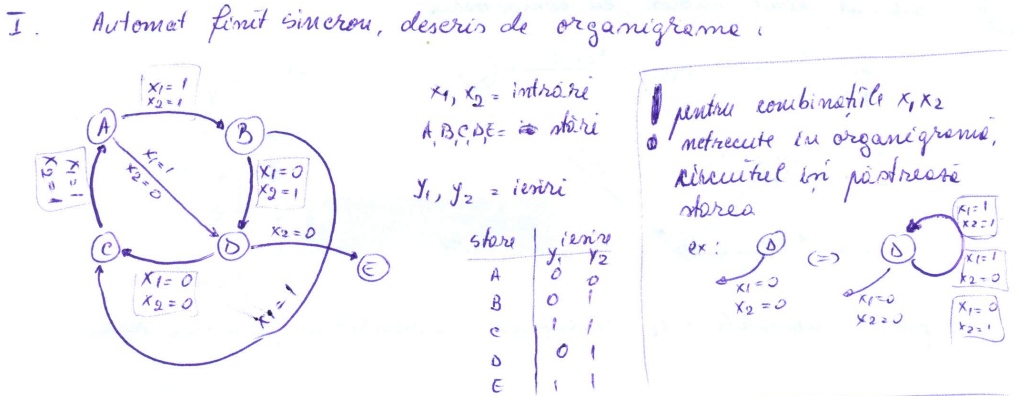

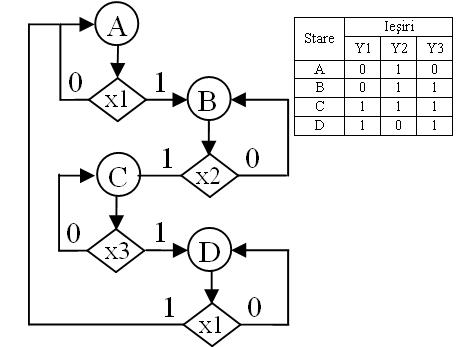

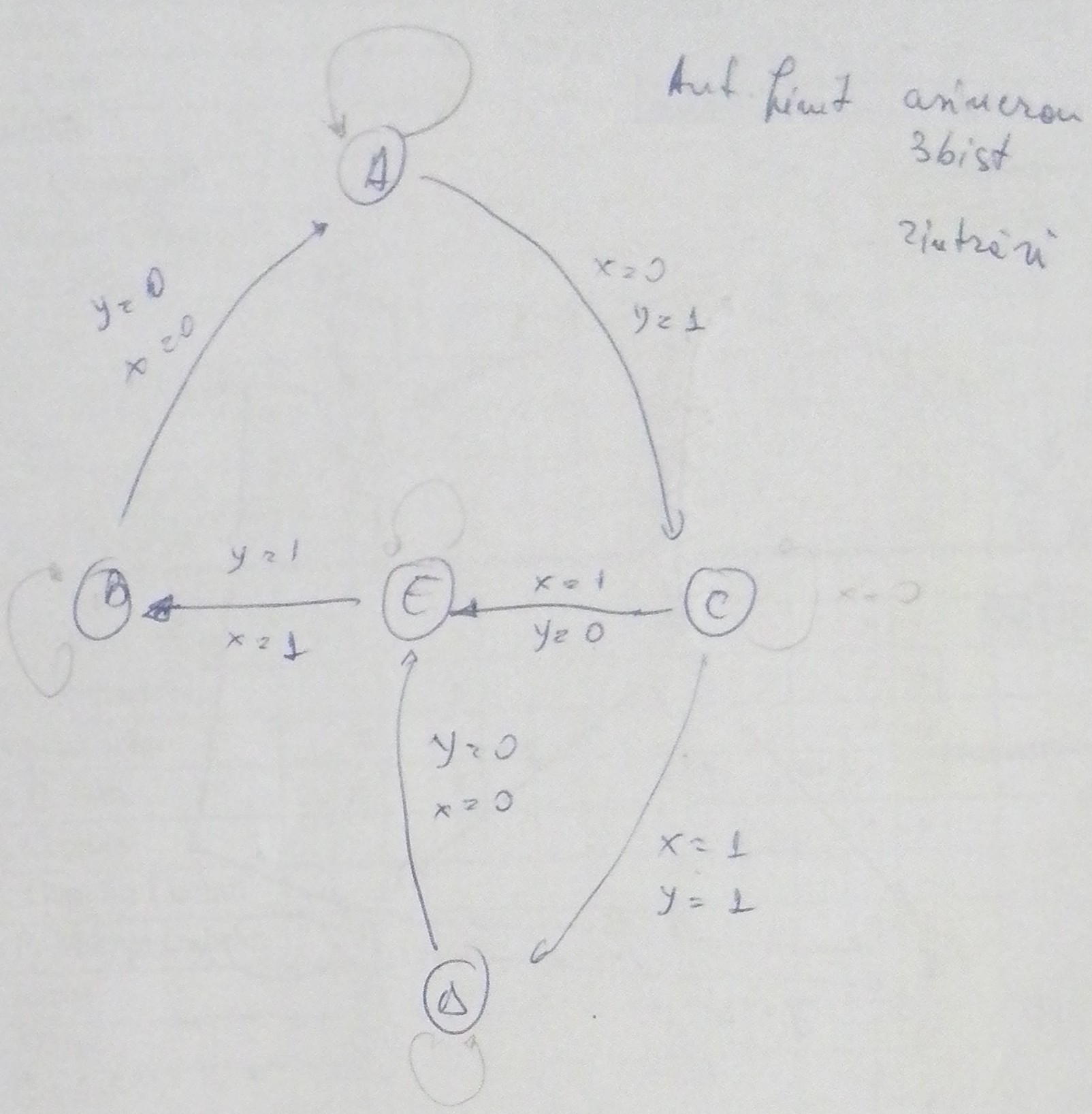

Automat finit 1.

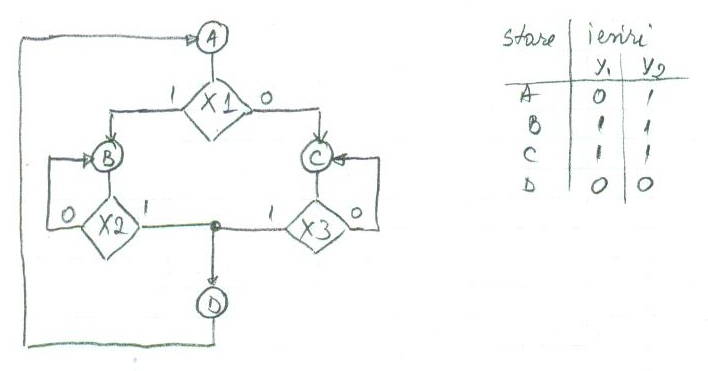

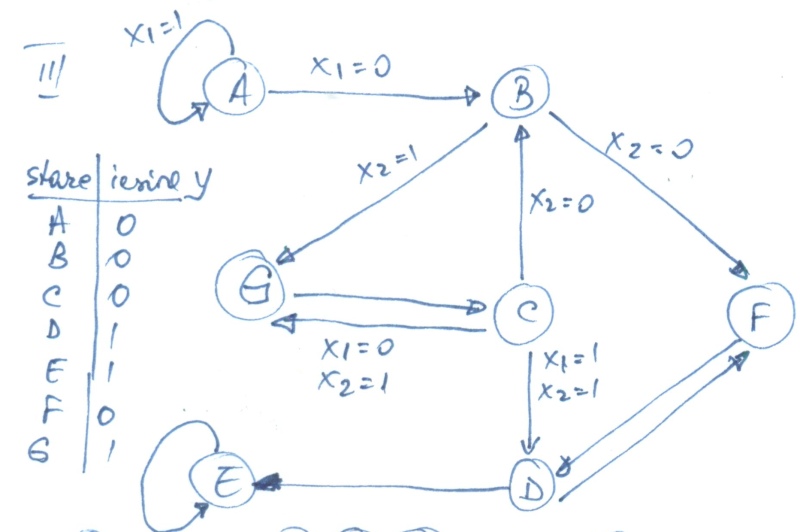

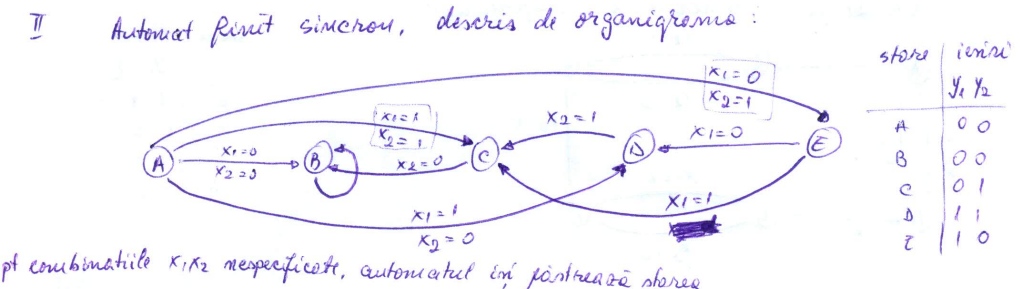

Automat finit 2.

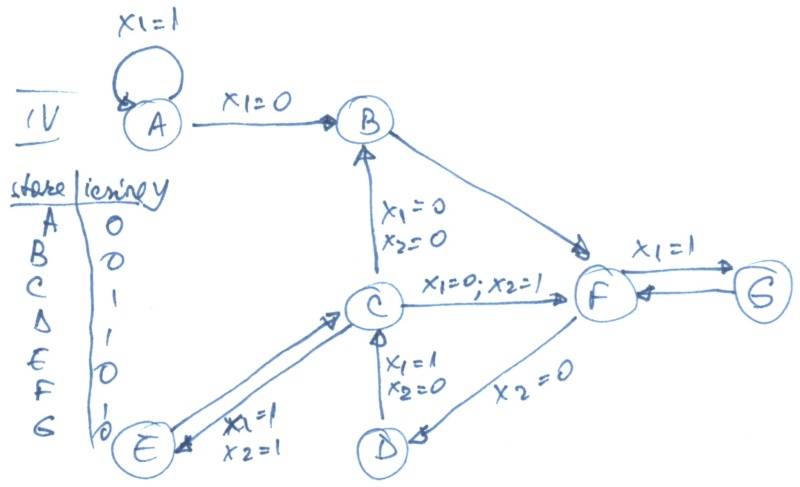

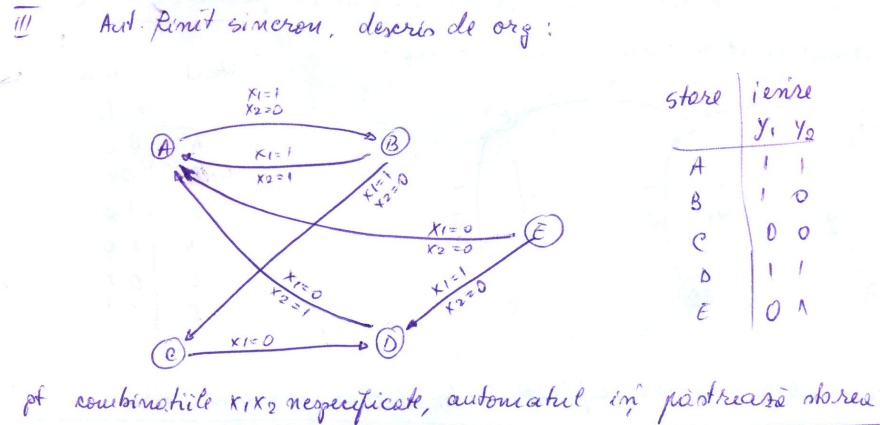

Automat finit 3.

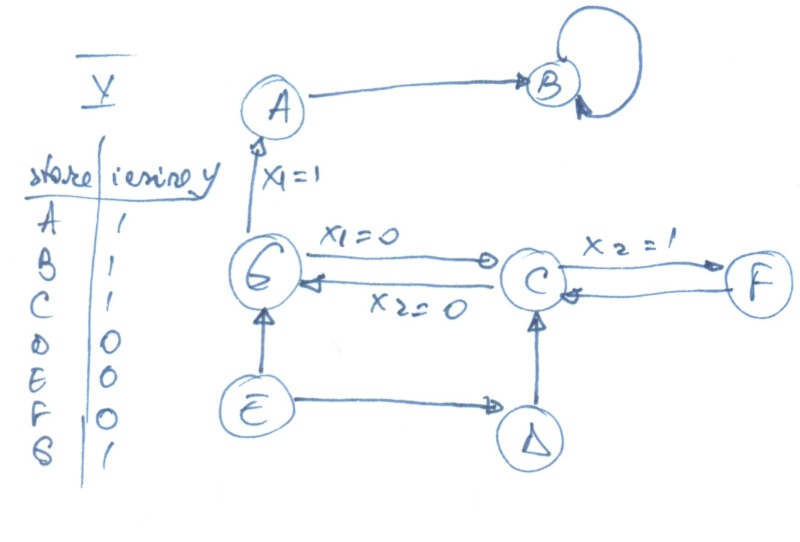

Automat finit 4.

Automat finit 5.

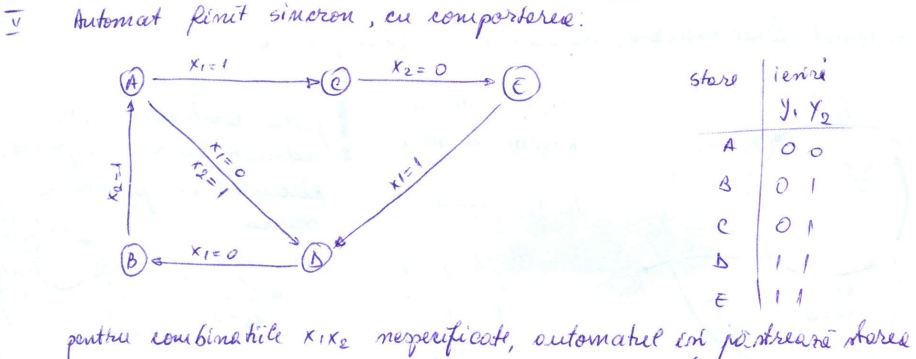

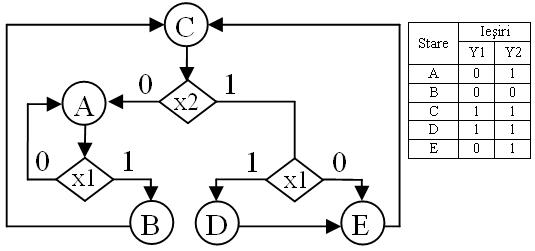

Automat finit 6.Cerinta: Sa se implementeze automatul finit din figura anterioara, utilizand doar:

1) circuite bistabile D si porti logice;

2) circuite bistabile D si porti logice SI/SI-nu;

3) circuite bistabile D si porti logice SAU/SAU-NU;

4) circuite bistabile D si multiplexoare;

5) circuite bistabile D si decodificatoare;

6) circuite bistabile JK si porti logice;

7) circuite bistabile JK si porti logice SI/SI-NU;

8) circuite bistabile JK si porti logice SAU/SAU-nu;

9) circuite bistabile JK si multiplexoare;

10) circuite bistabile JK si decodificatoare;

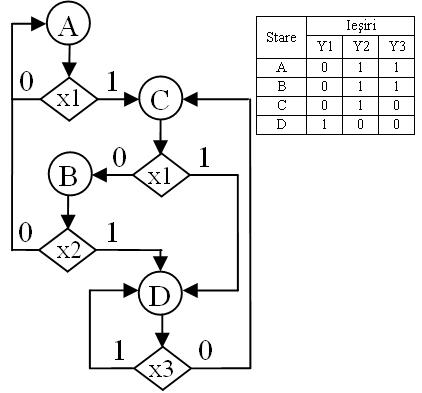

Anul universitar 2011-2012:

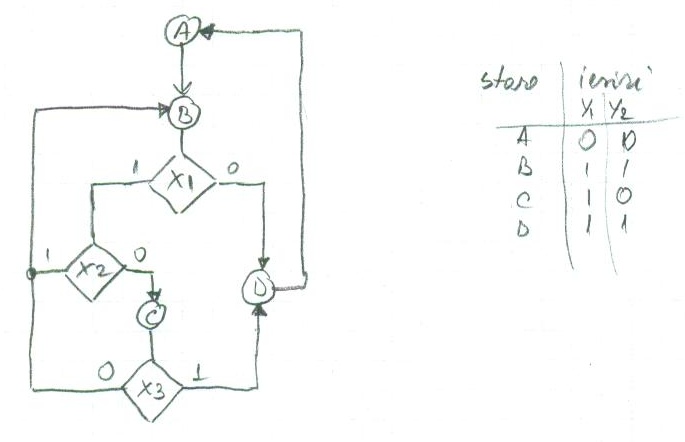

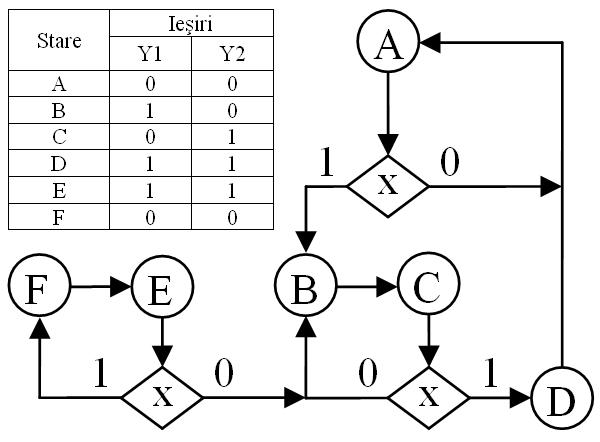

Cerinta: Sa se implementeze automatul finit din figura anterioara, utilizand doar:

1) circuite bistabile D si porti logice;

2) circuite bistabile D si porti logice SI/SI-nu;

3) circuite bistabile D si porti logice SAU/SAU-NU;

4) circuite bistabile D si multiplexoare;

5) circuite bistabile D si decodificatoare;

6) circuite bistabile JK si porti logice;

7) circuite bistabile JK si porti logice SAU/SAU-nu;

8) circuite bistabile JK si porti logice SI/SI-NU;

9) circuite bistabile JK si multiplexoare;

10) circuite bistabile JK si decodificatoare;

Anul universitar 2010-2011:

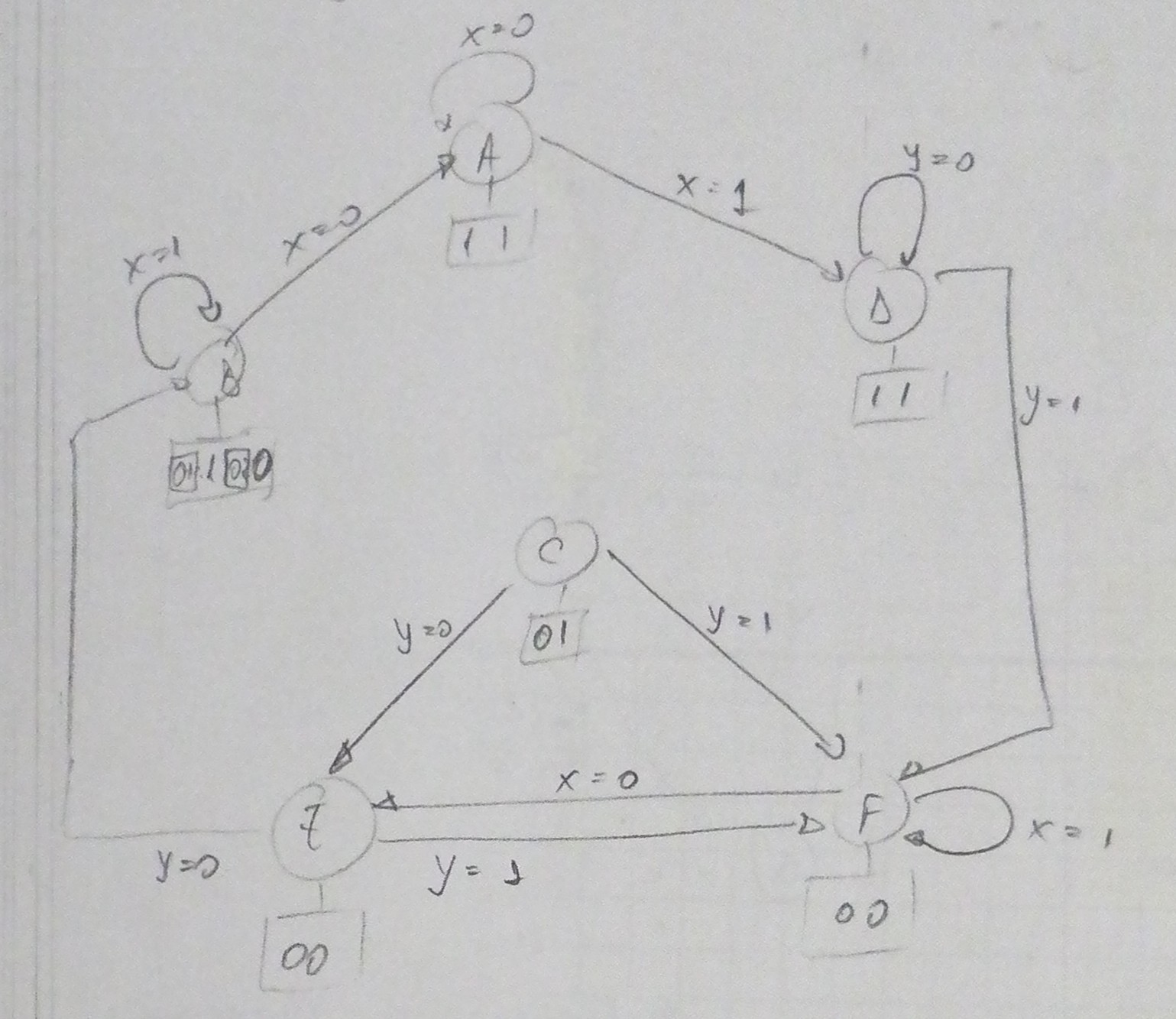

Automat finit 1.

Automat finit 2.

Automat finit 3.

Automat finit 4.

Automat finit 5.

Automat finit 6.

Automat finit 7.Cerinta: Sa se implementeze automatul fimit din figura anterioara, utilizand doar:

1) circuite bistabile D si porti logice;

2) circuite bistabile D si porti logice SAU/SAU-nu;

3) circuite bistabile D si porti logice SI/SI-NU;

4) circuite bistabile D si multiplexoare;

5) circuite bistabile D si decodificatoare;

6) circuite bistabile D si memorie ROM

7) circuite bistabile JK si porti logice;

8) circuite bistabile JK si porti logice SAU/SAU-nu;

9) circuite bistabile JK si porti logice SI/SI-NU;

10) circuite bistabile JK si multiplexoare;

11) circuite bistabile JK si decodificatoare;

12) circuite bistabile JK si memorie ROM

Anul universitar 2009-2010:

Cerinta: Sa se implementeze automatul fimit din figura anterioara, utilizand doar:

1) circuite bistabile D si porti logice;

2) circuite bistabile D si porti logice SAU/SAU-nu;

3) circuite bistabile D si porti logice SI/SI-NU;

4) circuite bistabile D si multiplexoare;

5) circuite bistabile D si decodificatoare;

6) circuite bistabile D si memorie ROM

7) circuite bistabile JK si porti logice;

8) circuite bistabile JK si porti logice SAU/SAU-nu;

9) circuite bistabile JK si porti logice SI/SI-NU;

10) circuite bistabile JK si multiplexoare;

11) circuite bistabile JK si decodificatoare;

12) circuite bistabile JK si memorie ROM

- Sa se realieze un circuit de comanda "half step" pentru un motor pas-cu-pas; reglarea curentului prin infasurari se va face prin modificarea factorului de umplere al curentului;

- Sa se proiecteze si sa se implementeze in FPGA (placa de dezvoltare Digilent Basys 2) un numarator "up/down" in domeniul 0-9999;

- Sa se proiecteze un circuit de alarma care nu se activeaza la introducerea corecta a codului de 6 cifre; implementare in FPGA;

- Sa se proiecteze o unitate aritmetico-logica pe 8 biti, cu instructiuni de adunare, scadere si inmultire; implementare in FPGA;

- Sa se proiecteze un turometru digital cu afisarea turatiei pe 2 cifre zecimale (se vor folosi afisoare cu 7 segmente);

- Sa se proiecteze o sirena cu 3 tonuri, pentru un circuit de alarma;

- Sa se proiecteze un sistem de lumini dinamice cu LED-uri (8-10 LED-uri, implementare in FPGA);

- Sa se proiecteze un circuit de alarma cu pornire intarziata (pentru usa frigiderului); implementare in FPGA;

- Sa se proiecteze un cronometru digital (afisarea timpului pe afisoare cu 7 segmente); implementare in FPGA;

- sa se proiecteze un stroboscop cu LED-uri de putere.